|

|

| 全加算器 |

| 辞書:科学用語の基礎知識 半導体用語編 (IYIC) |

| 読み:ぜん-かさんき |

| 外語:full adder |

| 品詞:名詞 |

2個の半加算器と1個のORゲートから構成される、繰り上がりを考慮した加算器のこと。

|

|

| 概要 |

全加算器は、2進数で、1桁の繰り上がりを含めた1桁の加算結果と、1桁の繰り上がりを出力することができる。

半加算器と比較して下の桁からの繰り上がりを加算できる機能を持っている。これにより、全加算器を必要な桁数組み合わせれば、任意桁の2進数の加算を実現できることになる。

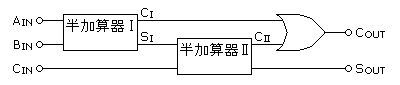

一つの全加算器は、二つの半加算器と一つのORゲートから構成される。そして、3入力(演算対象のA・Bと、繰り上がりのC)で、2出力(演算結果のSと、繰り上がりのC)となる。

| 特徴 |

| 構成 |

半加算器の場合、二つの結果を足す機能を持つ。ここで答えと繰り上がりが出力されるが、半加算器一個だけでは繰り上がりを更に足すことができない。

そこで、二つの結果を足すのに一個、その答えと繰り上がり桁を足すのに一個、合わせて二個あれば、一桁の計算が完全にこなせることになる。

このため、一桁を計算する回路を「全加算器」といい、その半分の機能を持つものを「半加算器」というのである。

そして例えば、8桁(8ビット)の加算器を実現するには、全加算器を8個(半加算器を16個)用意すれば良いことになる。

| 論理 |

三つの入力(入力A・Bと、繰り上がり桁Ci)を受け、一桁の答え(S)と一桁の繰り上がり(Co)を出力する。

| 入力 | 出力 | |||

|---|---|---|---|---|

| A | B | Ci | S | Co |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| 回路 |

全加算器

| リンク |

| 通信用語の基礎知識検索システム WDIC Explorer Ver 7.04a (27-May-2022) Search System : Copyright © Mirai corporation Dictionary : Copyright © WDIC Creators club |