| ア | イ | ウ | エ | オ |

| カ | キ | ク | ケ | コ |

| サ | シ | ス | セ | ソ |

| タ | チ | ツ | テ | ト |

| ナ | ニ | ヌ | ネ | ノ |

| ハ | ヒ | フ | ヘ | ホ |

| マ | ミ | ム | メ | モ |

| ヤ | ユ | ヨ | ||

| ラ | リ | ル | レ | ロ |

| ワ | ヰ | ヴ | ヱ | ヲ |

| ン |

| A | B | C | D | E |

| F | G | H | I | J |

| K | L | M | N | O |

| P | Q | R | S | T |

| U | V | W | X | Y |

| Z | 数字 | 記号 | ||

開発コードネーム3GIOとしてIntelにより開発され、PCI 3.0から仕様が盛り込まれた高速I/Oアーキテクチャー。

これは従来のPCIのパラレルバスインターフェイスと違い、ポイント・トゥー・ポイントのシリアルバスインターフェイス技術である。これは少ないピン数で高速な通信を実現するための工夫の一つといえる。

Intelによれば、1GHz前後がパラレルインターフェイスの限界であり、それ以上に転送レートを上げるためにはシリアルインターフェイスにせざるを得ない、としている。

詳細は後述するが、物理層速度と有効帯域は、それぞれ次の通りである。

標準速は1×、2倍速が2×、4倍速が4×となる。

なお上記は1方向あたりの速度であり、双方向つまり1レーンあたりの速度はこの倍となる。

PCI Expressの物理層プロトコルは、データ幅1ビット、0.8Vの差動駆動シリアルバスである。

標準速の1×では1レーンあたりの片方向ベアラー速度(物理層速度)は2.5Gbpsである。

これが8b/10b符号によりPLLのロックが保証(Embedded Clock Signaling)されるが、同時に符号化に伴い20%速度が減るので、標準速の1×では1レーンあたり片方向2.5Gbps×80%=2Gbps、つまり250Mバイト/秒となる。双方向合わせれば倍の500Mバイト/秒が有効帯域ということになる。

帯域(転送速度)と有効帯域を区別するため、物理層の速度は「2.5GT/秒」(GT=Giga transfers)のように表現されることがある。

なお、後述する2倍速(2×)や4倍速(4×)であれば、それぞれ1Gバイト/秒、2Gバイト/秒の有効帯域が実現されることになる。

従来の標準的なPCI(32ビット33MHzで133Mバイト/秒)と比較すると、1×の場合でも片方向で約2倍、双方向なら約4倍の帯域が実現されている。

PCI Expressでは、速度や帯域幅について、帯域とレーンという二種類の概念がある。表示は、帯域×レーンとし、帯域が1の時には帯域の表記を略す。

帯域は、2.5Gbps(片方向の物理層速度)を基準とする通信可能な容量(≒速度)である。1倍速、2倍速(5Gbps)、4倍速(10Gbps)などのデータレートが考慮されている。

最初に登場したPCI Express 1.0では1倍速のみ対応するが、複数のデータレート混在時のネゴシエーション規格も最初から存在する。2倍速はPCI Express 2.0から登場した。

PCI Express 1.0では、データレートの向上は未来技術とし、近い将来への拡張性として1×のまま複数レーンの同時使用による帯域拡大を可能としている。

レーンは、信号線の束数と考えると分かりやすい。信号線は片方向2本、双方向は倍の4本が単位であり、この双方向一組4本をレーン(lane)という最小単位として扱う。

必要に応じて1レーン(×1)、2レーン(×2)、4レーン(×4)、8レーン(×8)、12レーン(×12)、16レーン(×16)、32レーン(×32)が、仕様上存在する。しかしこの全てが実用化されるかといえば必ずしもそうではない。

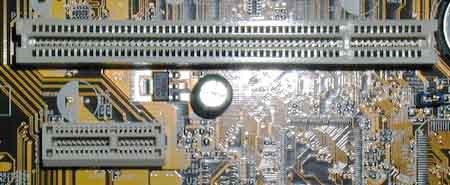

PCI Express ×1 写真の下/写真の上は通常のPCI

PCI Express ×16 写真の上/写真の下は通常のPCI

パソコン用の一般的なI/Oには1レーン(1×1、500Mバイト/秒)のものが、またグラフィックスカード用には16レーン(1×16、8Gバイト/秒)のものが、よく利用されている。

レーン数は多くも少なくもできるが、スロットのサイズが従来のPCIと近いものになる16レーンが手頃で、よく使われている。

1×16の場合、AGP 8×(2.132Gバイト/秒)の約4倍速となる。

PCI Expressでこの速度が実現されたことで、PCIの後継だったAGPの後継は、再びPCIの名を冠したPCI Expressに決定した。それでも、これはあくまで汎用バスなのであり、1×16をシリアルAGPなどと呼んだりはしない。グラフィック専用のAGPとは設計概念自体、異なるからである。

また、PCI Express 2.0からは倍速の2×16が、PCI Express 3.0からは4倍速の4×16がそれぞれ使用されるようになった。

4レーン(1×4、2Gバイト/秒)と8レーン(1×8、4Gバイト/秒)はサーバー機用の用途が考慮されていて、1×4はPCI-X 266相当、1×8はPCI-X 533相当である。

歴史的に、標準速(1×)の場合は1を略して単に×1、×4、×8、×16のように書かれることもある。

通常のコネクターでは、小さいスロットに大きなカードを挿すことはできない(逆は可能)が、内側の端が切り取られている「エッジフリー」タイプのコネクターを採用した製品もあり、この場合、×1や×4などに、大型の×16用カードを挿すことができる。ただし動作性能は挿したスロット相当に落ちる。

PCI Expressはプロトコルの階層構造(レイヤー構造)を採用した。

下から順に、次の5層に分けられている。

将来的に高速化などをする場合は、物理層だけを変えれば済むようになった。

またソフトウェア層以上では従来のPCIと互換性があり、ソフトウェアからは普通のPCIとして見える。このためPCIからの移行が容易である。これが、ハードウェアは全く別物であっても、PCIの名が冠されている最大の理由である。

コネクターは電源容量とは無関係にレーン数ごとにあり、レーン数が増えるごとに長くなる。

なお、より上位のスロットには、下位のカードを差し込むことが可能で、例えば×16の長いスロットに、エッジの短い×1のカードを挿すことができる。

PCIは5Vと3.3Vとがあったが、PCI Expressは3.3Vのみ。カードの長さに応じたスロットの違いはあるが、電圧の差異による違いは現時点では存在しない。

基板と端子は両面あるが、部品面をB面、はんだ面をA面という。

各レーンは、送信に3ピン、受信に3ピンを使う。送信/受信ともに4ピンずつ確保しており、余った1ピンにはGND、予備、あるいは別の機能を割り振っている。

最後に#が付く信号は、負論理信号を表わす。

| ピン | B面 | A面 | 機能 |

|---|---|---|---|

| 1 | +12V | PRSNT1# | カード挿入後はLOWにプルダウンされる |

| 2 | +12V | +12V | |

| 3 | RESERVED | +12V | |

| 4 | GND | GND | |

| 5 | SMCLK | TCK | SMBus/JTAG用ピン |

| 6 | SMDAT | TDI | |

| 7 | GND | TDO | |

| 8 | +3.3V | TMS | |

| 9 | TRST# | +3.3V | |

| 10 | +3.3Vaux | +3.3V | スタンバイ電源 |

| 11 | WAKE# | PWRGD | リンク再接続、パワーグッド |

| キーノッチ | |||

| 12 | RESERVED | GND | |

| 13 | GND | REFCLK+ | 基準クロック |

| 14 | HSOp(0) | REFCLK− | レーン0送信 |

| 15 | HSOn(0) | GND | |

| 16 | GND | HSIp(0) | レーン0受信 |

| 17 | PRSNT2# | HSIn(0) | |

| 18 | GND | GND | |

ここまでは、レーン数を問わず共通。以下、×4の場合を例示する。

| 19 | HSOp(1) | RESERVED | レーン1送信 |

|---|---|---|---|

| 20 | HSOn(1) | GND | |

| 21 | GND | HSIp(1) | レーン1受信 |

| 22 | GND | HSIn(1) | |

| 23 | HSOp(2) | GND | レーン2送信 |

| 24 | HSOn(2) | GND | |

| 25 | GND | HSIp(2) | レーン2受信 |

| 26 | GND | HSIn(2) | |

| 27 | HSOp(3) | GND | レーン3送信 |

| 28 | HSOn(3) | GND | |

| 29 | GND | HSIp(3) | レーン3受信 |

| 30 | RESERVED | HSIn(3) | |

| 31 | PRSNT2# | GND | |

| 32 | GND | RESERVED |

×8や×16の場合は、4レーンごとに、伸ばされていくことになる。

×8や×16の場合は次がある。

| 33 | HSOp(4) | RESERVED | レーン4送信 |

|---|---|---|---|

| 34 | HSOn(4) | GND | |

| 35 | GND | HSIp(4) | レーン4受信 |

| 36 | GND | HSIn(4) | |

| 37 | HSOp(5) | GND | レーン5送信 |

| 38 | HSOn(5) | GND | |

| 39 | GND | HSIp(5) | レーン5受信 |

| 40 | GND | HSIn(5) | |

| 41 | HSOp(6) | GND | レーン6送信 |

| 42 | HSOn(6) | GND | |

| 43 | GND | HSIp(6) | レーン6受信 |

| 44 | GND | HSIn(6) | |

| 45 | HSOp(7) | GND | レーン6送信 |

| 46 | HSOn(7) | GND | |

| 47 | GND | HSIp(7) | レーン7受信 |

| 48 | PRSNT#2 | HSIn(7) | |

| 49 | GND | GND |

×16の場合はさらに次がある。

| 50 | HSOp(8) | RESERVED | レーン8送信 |

|---|---|---|---|

| 51 | HSOn(8) | GND | |

| 52 | GND | HSIp(8) | レーン8受信 |

| 53 | GND | HSIn(8) | |

| 54 | HSOp(9) | GND | レーン9送信 |

| 55 | HSOn(9) | GND | |

| 56 | GND | HSIp(9) | レーン9受信 |

| 57 | GND | HSIn(9) | |

| 58 | HSOp(10) | GND | レーン10送信 |

| 59 | HSOn(10) | GND | |

| 60 | GND | HSIp(10) | レーン10受信 |

| 61 | GND | HSIn(10) | |

| 62 | HSOp(11) | GND | レーン11送信 |

| 63 | HSOn(11) | GND | |

| 64 | GND | HSIp(11) | レーン11受信 |

| 65 | GND | HSIn(11) | |

| 66 | HSOp(12) | GND | レーン12送信 |

| 67 | HSOn(12) | GND | |

| 68 | GND | HSIp(12) | レーン12受信 |

| 69 | GND | HSIn(12) | |

| 70 | HSOp(13) | GND | レーン13送信 |

| 71 | HSOn(13) | GND | |

| 72 | GND | HSIp(13) | レーン13受信 |

| 73 | GND | HSIn(13) | |

| 74 | HSOp(14) | GND | レーン14送信 |

| 75 | HSOn(14) | GND | |

| 76 | GND | HSIp(14) | レーン14受信 |

| 77 | GND | HSIn(14) | |

| 78 | HSOp(15) | GND | レーン15送信 |

| 79 | HSOn(15) | GND | |

| 80 | GND | HSIp(15) | レーン15受信 |

| 81 | PRSNT#2 | HSIn(15) | |

| 82 | RSVD#2 | GND |

PCI Expressの対抗としては、パラレルPCIの拡張であるPCI-Xがある。

また、スパコンなどの分野で活躍するInfiniBandも、元々はPCIの後継を標榜していたもので、PCI Expressの対抗といえる。

コメントなどを投稿するフォームは、日本語対応時のみ表示されます